Troubleshooting Analog to Digital Converter Offset using a Mixed Signal Oscilloscope

# APPLICATION NOTE

### Introduction

In a traditional acquisition system, an analog signal input goes through some form of signal conditioning circuitry before being sampled by an analog to digital converter (ADC). The number of bits used by the ADC determines the vertical resolution of your sampled signal.

Any ADC system must accurately convert analog signals into digital values with a specified range (or gain) and offset. Linearity is also a critical DC specification for an ADC. It is common to use a ramp generator to provide a predictable source to evaluate the gain, offset and linearity of an ADC system.

#### THIS APPLICATION NOTE

- Explains how an MSO may be used to troubleshoot and debug ADC systems

- Explains how to use an MSO's digital channels and parallel bus decode capability to provide greater insight into how an ADC system behaves

- Explains how to use Wave Inspector<sup>®</sup> navigation to locate specific events within long waveform captures and display them clearly

The ability to present both analog and digital representations of signals simultaneously makes mixed signal oscilloscopes (MSOs) ideal for verifying and debugging digital circuits. Features like parallel and serial bus trigger and decode further aid in the design and debug process. The Tektronix 5 Series MSO, equipped with a TLP058 logic probe, is used to demonstrate using an MSO to troubleshoot an unexpected offset error in an analog-to-digital converter.

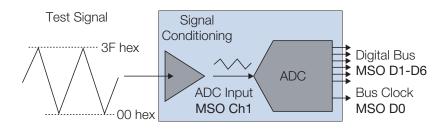

# The Test Setup

In this example, the acquisition system under test is comprised of an analog signal conditioning circuit that feeds a 20MS/s, 6-bit analog to digital converter (ADC). The test ramp signal is designed to utilize the entire vertical range of the 6-bit ADC from 00 to 3F hex. Channel 1 of the 5 Series MSO will monitor the test ramp between the signal conditioning and ADC stages of the acquisition system. The six digital outputs from the ADC, along with the parallel bus clock, will be captured using the new TLP058 logic probe. As shown in the image above, the TLP058 plugs into a FlexChannel input on the 5 Series MSO. (Note that Channel 2 will not be used in this application.) On the logic probe, D0 will monitor the bus clock while digital channels D1-D6 monitor the ADC digital outputs.

# Decoding digital ADC outputs

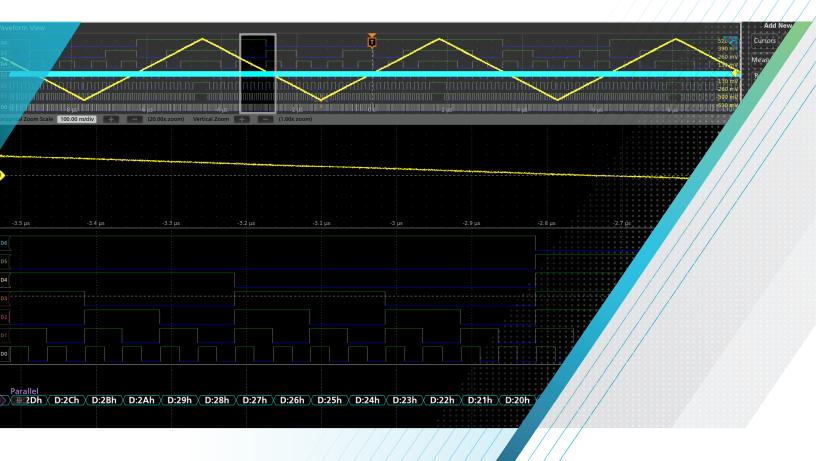

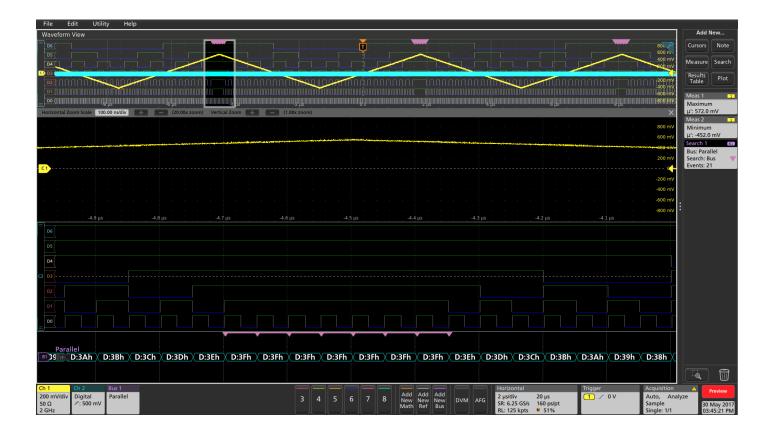

The Wave Inspector zoom is set to 20x magnification to clearly show each individual decoded value from the 6-bit parallel bus ADC output. The zoom overview at the top of the screen shows the overall stimulus and response. The magnified regions for both the analog and digital channels are in the zoom view below. A parallel bus, made up of the six data bits and clocked on the falling edge of the clock (D0) is set up at the bottom of the display. The parallel bus is configured to display in hexadecimal.

The Wave Inspector pan capability allows us to move the position of the zoom box through the waveform capture to inspect each decoded bus value. In this case, the ADC codes appear to change smoothly and predictably in response to the ramp input.

# Debugging with Wave Inspector Search and Mark

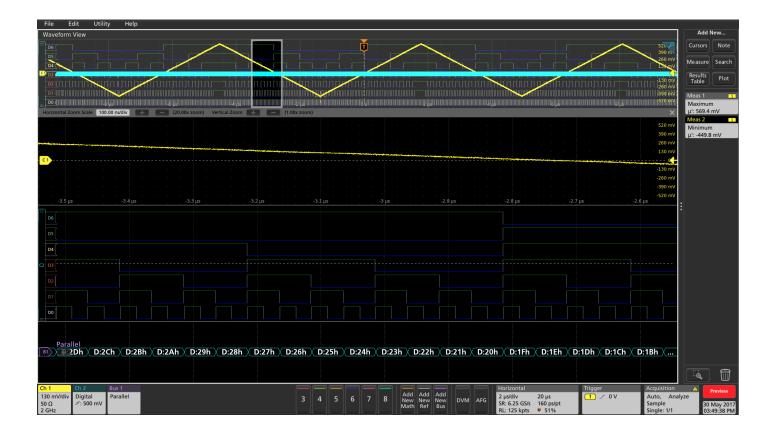

A cursory analysis of the ADC response suggests good linearity, but all is not well. We need to confirm that our test ramp signal is exercising all available digital sample values from our ADC correctly. Looking at the entire waveform capture in the zoom overview, three distinct valleys are visible. Assuming the acquisition system is operating properly, there should be three 00 hex values in the decoded parallel bus.

Wave Inspector's Search and Mark function may be used to quickly find and identify specific data values or events in a waveform capture. In this case the search function it is configured to look for all occurrences of 00 hex. Surprisingly, as shown by the empty value in the Search Badge, there are no 00 hex values in the entire waveform capture. No 00 hex values means the ADC did not sample any analog input voltage corresponding to the minimum 00 hex value. This indicates the analog signal conditioning circuit in the acquisition system did not correctly process the minimum peaks of the test ramp signal to match the minimum ADC input voltage value in order for the ADC to produce a 00 hex output.

Reconfiguring the Wave Inspector Search and Mark for the maximum ADC output value of 3F yields 21 results. This should throw up warning flags, as there should only be three 3F values, one for each test signal peak. Looking at the zoom overview, the marks for the 3F values are grouped in three bunches over each test ramp peak. The zoom view over the decoded parallel bus values shows the expected progression of values 3A, 3B, 3C, 3D, 3E, up to 3F where instead of a single value there are seven.

There is no clear evidence that the analog test signal is incorrect, and we clearly see the defined point for each signal peak. This indicates that the test ramp signal maximum voltage exceeds the maximum voltage input of the ADC and is subsequently clipping. Also, remember that the previous search did not find any minimum 00 hex values.

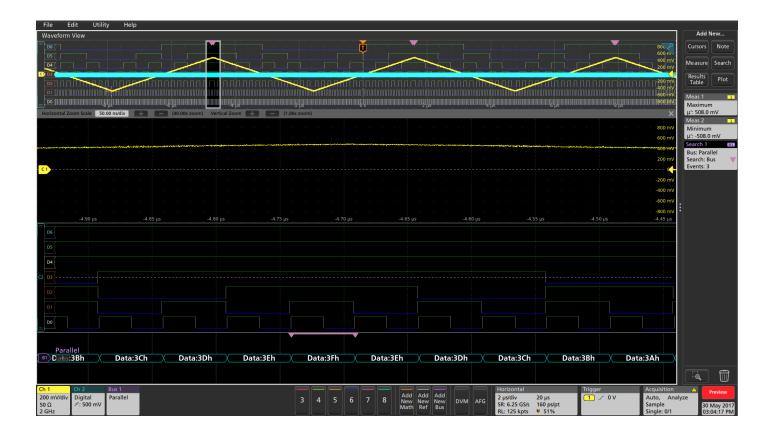

Measurements of the peak voltages between the signal conditioner and ADC point to the problem. The maximum and minimum voltage values for the signal conditioner output are 572 mV and -452 mV respectively. The signal conditioning circuit offset and gain need to be adjusted to eliminate the DC shift and clipping issues.

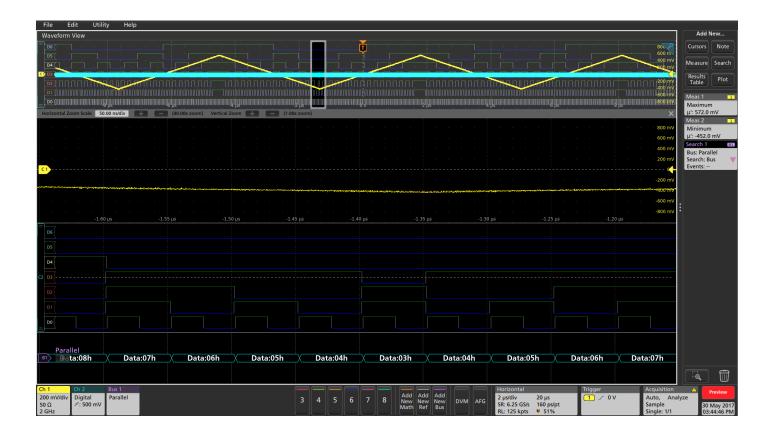

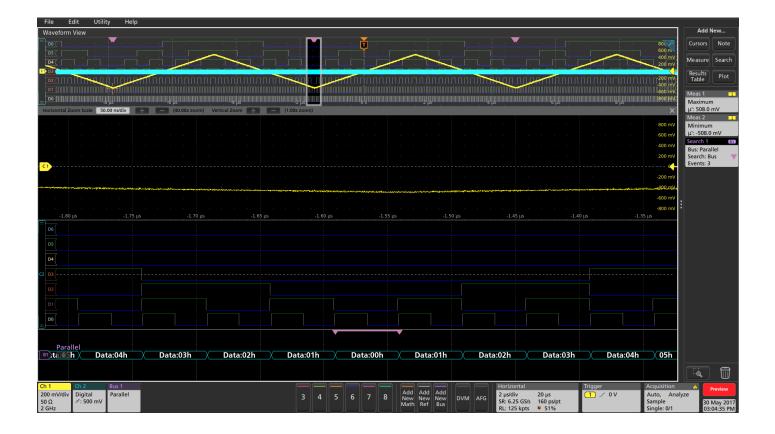

After adjusting the gain and offset of the signal conditioning circuit, the ADC input waveform maximum and minimum is now a symmetrical 508 mV and -508 mV respectively. There is now a single 3F hex value at each test ramp peak as expected. The maximum input of the ADC is now correctly sampled.

Configuring Wave Inspector to search for 00 hex values yields the expected results as well. There are now three 00 hex values found in the waveform record, one for each test ramp valley. The signal conditioning circuit adjustments resolved the issue, and the test ramp now correctly exercises each available digitizing level in the 6-bit Analog to Digital Converter.

The digital channels and bus decode capability of a mixed signal oscilloscope can be invaluable when troubleshooting Analog to Digital systems. Being able to use pan and zoom allows you to observe very short duration events within the acquisition record, while still showing the entire waveform capture for reference. Knowing how to use search and mark capabilities can help you quickly verify the location (or lack thereof) of specific decoded bus values.

#### **Contact Information:**

Australia\* 1 800 709 465 Austria 00800 2255 4835 Balkans, Israel, South Africa and other ISE Countries +41 52 675 3777 Belgium\* 00800 2255 4835 Brazil +55 (11) 3759 7627 Canada 1 800 833 9200 Central East Europe / Baltics +41 52 675 3777 Central Europe / Greece +41 52 675 3777 Denmark +45 80 88 1401 Finland +41 52 675 3777 France\* 00800 2255 4835 Germany\* 00800 2255 4835 Hong Kong 400 820 5835 India 000 800 650 1835 Indonesia 007 803 601 5249 Italy 00800 2255 4835 Japan 81 (3) 6714 3010 Luxembourg +41 52 675 3777 Malaysia 1 800 22 55835 Mexico, Central/South America and Caribbean 52 (55) 56 04 50 90 Middle East, Asia, and North Africa +41 52 675 3777 The Netherlands\* 00800 2255 4835 New Zealand 0800 800 238 Norway 800 16098 People's Republic of China 400 820 5835 Philippines 1 800 1601 0077 Poland +41 52 675 3777 Portugal 80 08 12370 Republic of Korea +82 2 6917 5000 Russia / CIS +7 (495) 6647564 Singapore 800 6011 473 South Africa +41 52 675 3777 Spain\* 00800 2255 4835 Sweden\* 00800 2255 4835 Switzerland\* 00800 2255 4835 Taiwan 886 (2) 2656 6688 Thailand 1 800 011 931 United Kingdom / Ireland\* 00800 2255 4835 USA 1 800 833 9200 Vietnam 12060128

\* European toll-free number. If not accessible, call: +41 52 675 3777

Find more valuable resources at TEK.COM

Copyright © Tektronix. All rights reserved. Tektronix products are covered by U.S. and foreign patents, issued and pending. Information in this publication supersedes that in all previously published material. Specification and price change privileges reserved. TEKTRONIX and TEK are registered trademarks of Tektronix, Inc. All other trade names referenced are the service marks, trademarks or registered trademarks of their respective companies. 09/17 EA 55W-61096-0